Ideias, informações e conhecimentos compartilhados pela equipe

de Investigação, Desenvolvimento e Inovação da BASE4 Security.

Técnicas de detecção de Trojans em implementações de hardware

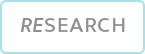

Em 2018 fomos surpreendidos com a notícia de que a Amazon três anos atrás tinha começado a avaliar discretamente uma startup chamada Elementar, que seria uma aquisição estratégica para ajudar na expansão de seu serviço de streaming de vídeo, hoje conhecido como Amazon Prime Video. A Elemental criou um software para compactar arquivos de vídeo enormes e formatá-los para diferentes dispositivos. Sua tecnologia ajudou a transmitir os Jogos Olímpicos online, a se comunicar com a Estação Espacial Internacional e a canalizar imagens de drones para a Agência Central de Inteligência. A AWS, que supervisionava a possível aquisição, contratou uma empresa externa para analisar a segurança da empresa. Primeiro, analisamos seu produto principal: os servidores caros que os clientes instalavam em suas redes para lidar com a compactação de vídeo. Esses servidores foram montados para a Elemental pela Supermicro Computer Inc. que é um dos maiores fornecedores mundiais de placas-mãe para servidores.

Mas durante a investigação encontraram um pequeno microchip, que não fazia parte do projeto original dos PCBs. A Amazon relatou a descoberta às autoridades dos EUA, causando um arrepio na comunidade de inteligência, já que os servidores da Elemental podem ser encontrados em data centers do Departamento de Defesa, operações de drones da CIA e redes a bordo de navios de guerra da Marinha. A Elemental era apenas uma das centenas de clientes da Supermicro.

Os pesquisadores determinaram que o microchip permitia que os invasores criassem uma porta “stealth” em qualquer rede que incluísse os servidores hackeados. Presume-se que os chips tenham sido instalados em fábricas administradas por empresas terceirizadas na China.

Esse tipo de ataque foi um pouco mais sério do que os incidentes baseados em software que estamos acostumados a ver. Hacks de hardware são mais difíceis de conseguir e potencialmente mais devastadores, permitindo acesso de longo prazo a qualquer tipo de empresa que implemente essas soluções.

Existem duas maneiras de alterar o interior de um computador. Um, conhecido como interdição, consiste no manuseio de dispositivos que estão em trânsito do fabricante para o cliente. As agências de espionagem dos EUA são favorecidas com esse método, de acordo com documentos vazados pelo ex-prestador de serviços da NSA, Edward Snowden.

O outro método envolve modificações de fabricação. Um país em particular tem a vantagem de executar esse tipo de ataque: a China, que, segundo algumas estimativas, produz 75% dos telefones celulares do mundo e 90% dos PCs. Ainda assim, conseguir um ataque de “sowing”significa desenvolver um profundo conhecimento do design de um produto, manipulá-lo sem afetar suas funções ou componentes e fazê-lo dentro da fábrica em tempo recorde, e não menos importante garantir que esses dispositivos passem despercebidos por uma grande cadeia logística global até chegarem ao local desejado.

Finalmente, esses pesquisadores descobriram que eventualmente esse ataque de “sowing” afetou quase 30 empresas, incluindo um grande banco, empreiteiras do governo e a empresa mais valiosa do mundo, a Apple. A Apple era um grande cliente da Supermicro e planejava encomendar mais de 30.000 de seus servidores em dois anos para uma nova rede global de centros de dados. Três especialistas seniores da Apple dizem que no verão de 2015, chips maliciosos também foram encontrados em placas-mãe da Supermicro. A Apple então cortou os laços com a Supermicro no ano seguinte, mas eles descreveram suas causas como razões não relacionadas.

O governo chinês não abordou diretamente as questões sobre a adulteração dos servidores da Supermicro, emitindo uma declaração que dizia, em parte, "A segurança da cadeia de suprimentos no ciberespaço é uma preocupação comum, e a China também é uma vítima”. O FBI e o Escritório do Diretor de Inteligência Nacional, em nome da CIA e da NSA, se recusaram a comentar.Hoje, a Supermicro vende mais placas-mãe para servidores do que quase qualquer outra empresa no mundo. Também domina o mercado para PCBs usados em computadores especiais, desde máquinas de ressonância magnética até sistemas de armas. Suas placas-mãe podem ser encontradas em configurações de servidor personalizadas em bancos, fundos de hedge, provedores de computação em nuvem e serviços de hospedagem na web, entre outros lugares. A Supermicro tem instalações de montagem na Califórnia, Holanda e Taiwan, mas suas placas-mãe são quase todas fabricadas por empreiteiras na China.

Presente

Embora até a data em que escrevo este post, quase uma década se passou desde a investigação acima mencionada e mais de meio século desde que o termo Trojan, ou melhor, cavalo de Tróia, foi usado pela primeira vez em um relatório da Força Aérea dos EUA na pós-graduação “Multics Security Evaluation: Vulnerability Analysis" que mencionava como pequenos blocos de código poderiam afetar o hardware dos sistemas de controle de acesso, fazendo-se passar por algo que não eram, atualmente detectar Trojans em hardware tornou-se uma dificuldade, pois estes não são mais apenas encontrados em um ”microchip” extra anexado a um PCB, caso contrário, os pequenos transistores que compõem o “microchip desonesto” podem ser incorporados na matriz de silício dos processadores e chipset de destino.

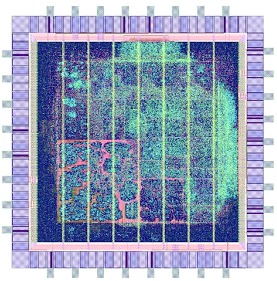

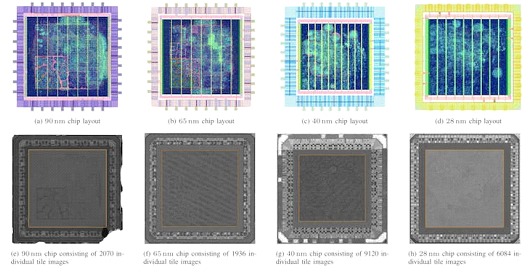

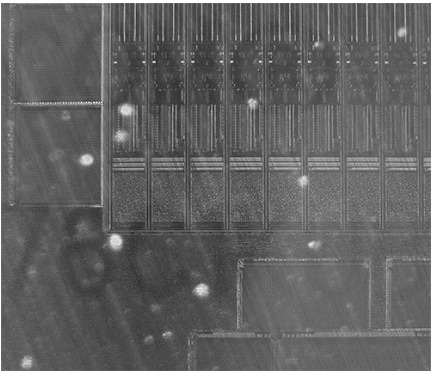

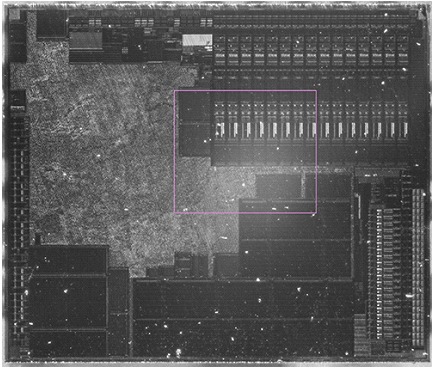

Usando milhares de imagens de microscópio eletrônico e comparando-as com o design original do chip, pesquisadores da Ruhr University Bochum e do Max Planck Institute for Security and Privacy (MPI-SP) desenvolveram uma abordagem para analisar fotos de matrizes de microchips. Para revelar ataques de cavalos de Tróia em nosso hardware, eles não apenas estão obtendo bons resultados, mas também estão disponibilizando suas imagens e algoritmos para que pesquisadores independentes possam experimentar.

"É concebível que pequenas mudanças possam ser inseridas nos projetos da fábrica pouco antes da produção, o que poderia tornar as matrizes inseguras", diz Steffen Becker, co-autor do artigo detalhando o trabalho. “Em casos extremos, esses cavalos de Tróia de hardware podem permitir que um invasor prejudique partes da infraestrutura de telecomunicações com o apertar de um botão”.

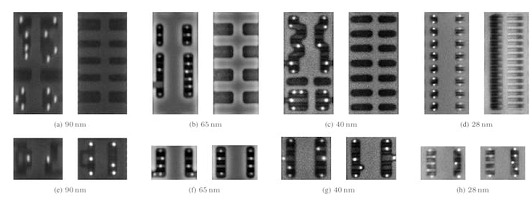

Olhando para os chips construídos em processos de 28 nm, 40 nm, 65 nm e 90 nm, a equipe começou a automatizar o processo de inspeção desses chips. Usando projetos criados por Thorben Moos, eles descobriram uma maneira de testar sua abordagem: "Comparar as imagens dos chips e os planos de construção acabou sendo um grande desafio, porque primeiro tivemos que sobrepor os dados com precisão", diz o primeiro autor Endres Puschner . "No menor chip, que tem 28 nanômetros de tamanho, uma única partícula de poeira ou cabelo pode obscurecer uma fileira inteira de células padrão."

Apesar desses desafios, o algoritmo de análise se mostrou promissor, detectando automaticamente 37 das 40 modificações feitas para o teste, incluindo aquelas feitas em chips construídos em processos entre 40nm e 90nm. O algoritmo certamente retornou 500 falsos positivos – mas, diz Puschner, “com mais de 1,5 milhão de células padrão examinadas, esta é uma taxa muito boa”.

Se você quiser fazer seus próprios testes no final deste post, não se esqueça de ver as referências, onde você pode encontrar o documento da equipe e o código usado que foi publicado no GitHub sob a Licença Permissiva do MIT.

Técnicas Atuais

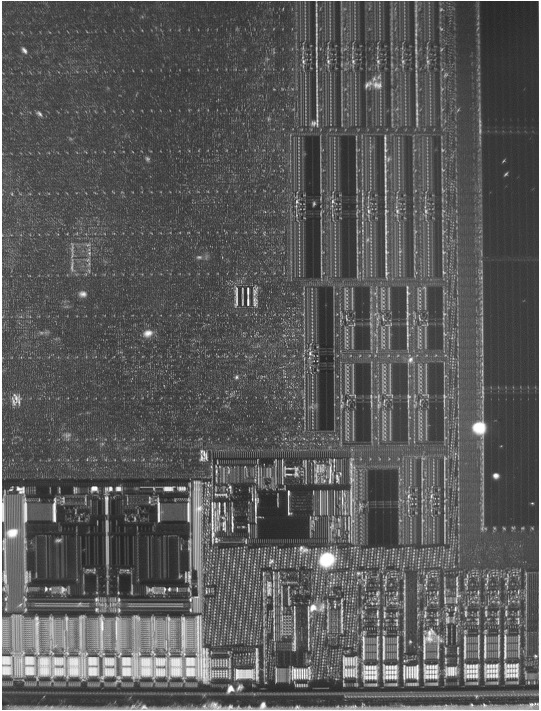

Hoje existem muitas opções para inspecionar a construção do chip; no entanto, todas essas técnicas têm um problema de “tempo de verificação versus tempo de uso”. Em outras palavras, nenhuma dessas técnicas é in situ. Eles devem ser feitos em amostras de chip que sejam meramente representativas do dispositivo, ou devem ser feitos em instalações remotas para que a amostra passe pelas mãos de muitos estranhos antes de retornar ao seu proprietário. A microscopia eletrônica de varredura (SEM), exemplificada acima, é um método popular de inspeção de chips. A técnica pode produzir imagens altamente detalhadas até mesmo dos mais recentes transistores em escala nanométrica. No entanto, a técnica é destrutiva: ela só pode sondar a superfície de um material. Para transistores de imagem, deve-se remover as camadas superiores do pacote por meio de técnicas como decapagem até o metal. Portanto, a técnica não é adequada para uma inspeção no local.

Os raios-X, além de possuírem os instrumentos e proteções correspondentes, não são destrutivos e são capazes de realizar uma inspeção no local. No entanto, o silício é quase transparente aos tipos de raios-X normalmente usados, pode ser usado para identificar o tamanho das seções e a posição dos fios de ouro que viajam das almofadas até a matriz de silício, mas não pode nos dar informações sobre o padrão dos transistores.

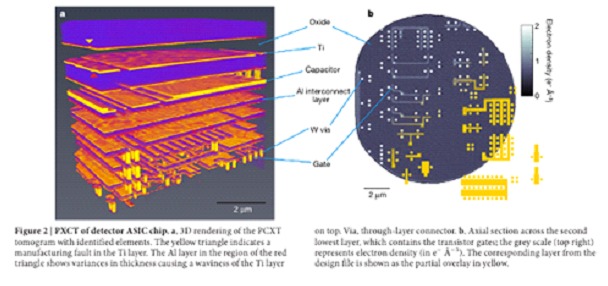

Por outro lado, a tipografia de raios-X é uma técnica que usa raios-X de alta energia que podem definir de forma não destrutiva o padrão dos transistores em um chip. A imagem a seguir é um exemplo de uma imagem 3D de alta resolução gerada pela técnica, conforme revelado no artigo “Imagem tridimensional não destrutiva de alta resolução de circuitos integrados”

É uma técnica muito poderosa, mas infelizmente requer uma fonte de luz do tamanho de um edifício, como a Swiss Light Source (SLS) (edifício em forma de rosquinha na foto), que há poucas no mundo. Embora seja um método poderoso, não é prático inspecionar todos os dispositivos, muito menos um usuário final.

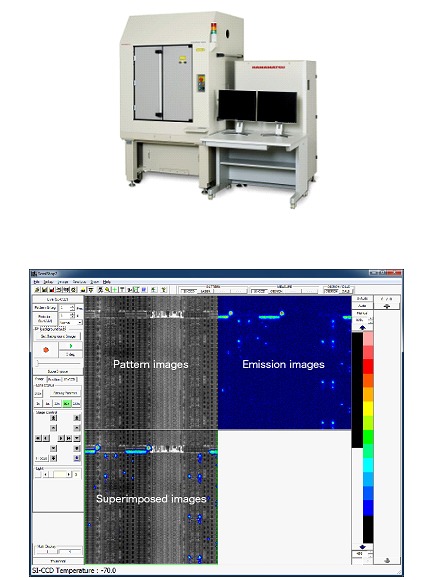

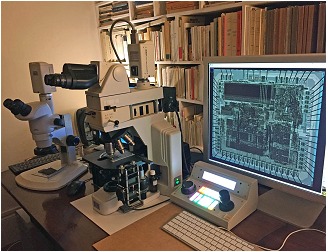

Algumas empresas desenvolveram "Laboratórios Portáteis" como é o caso da Hamamatsu com seu Microscópio de emissão PHEMOS-1000 , e o descreve como um microscópio de alta resolução que identifica locais de falha em dispositivos semicondutores, detectando emissões de luz fraca e emissões de calor causadas por defeitos em dispositivos semicondutores. Pode ser equipado com um sistema de varredura a laser opcional e permite a aquisição de imagens de padrão de alta resolução.

Esta última parece uma solução ideal, mas infelizmente é um aparelho que junto com seus acessórios chega a um valor de U$ 1M, por isso é bastante restrito ao público.

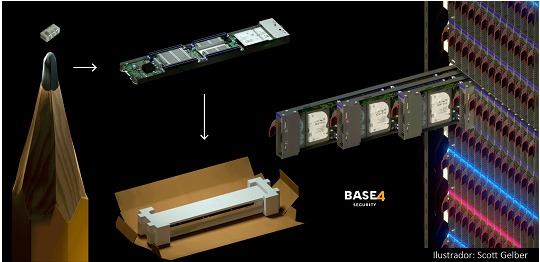

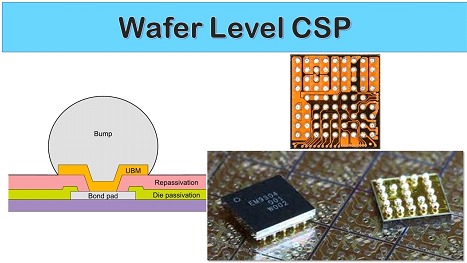

Felizmente, no mundo dos chips, tornou-se cada vez mais popular encapsular chips sem plástico moldado. A desvantagem de expor os delicados chips de silício a possíveis abusos mecânicos é compensada pelo desempenho térmico aprimorado, melhores características elétricas e custos geralmente mais baixos em comparação com a sobre moldagem. Devido às suas vantagens atraentes, esse estilo de embalagem é onipresente em dispositivos móveis. Esse tipo de embalagem é comumente conhecido como WLCSP ou embalagem em nível de wafer.

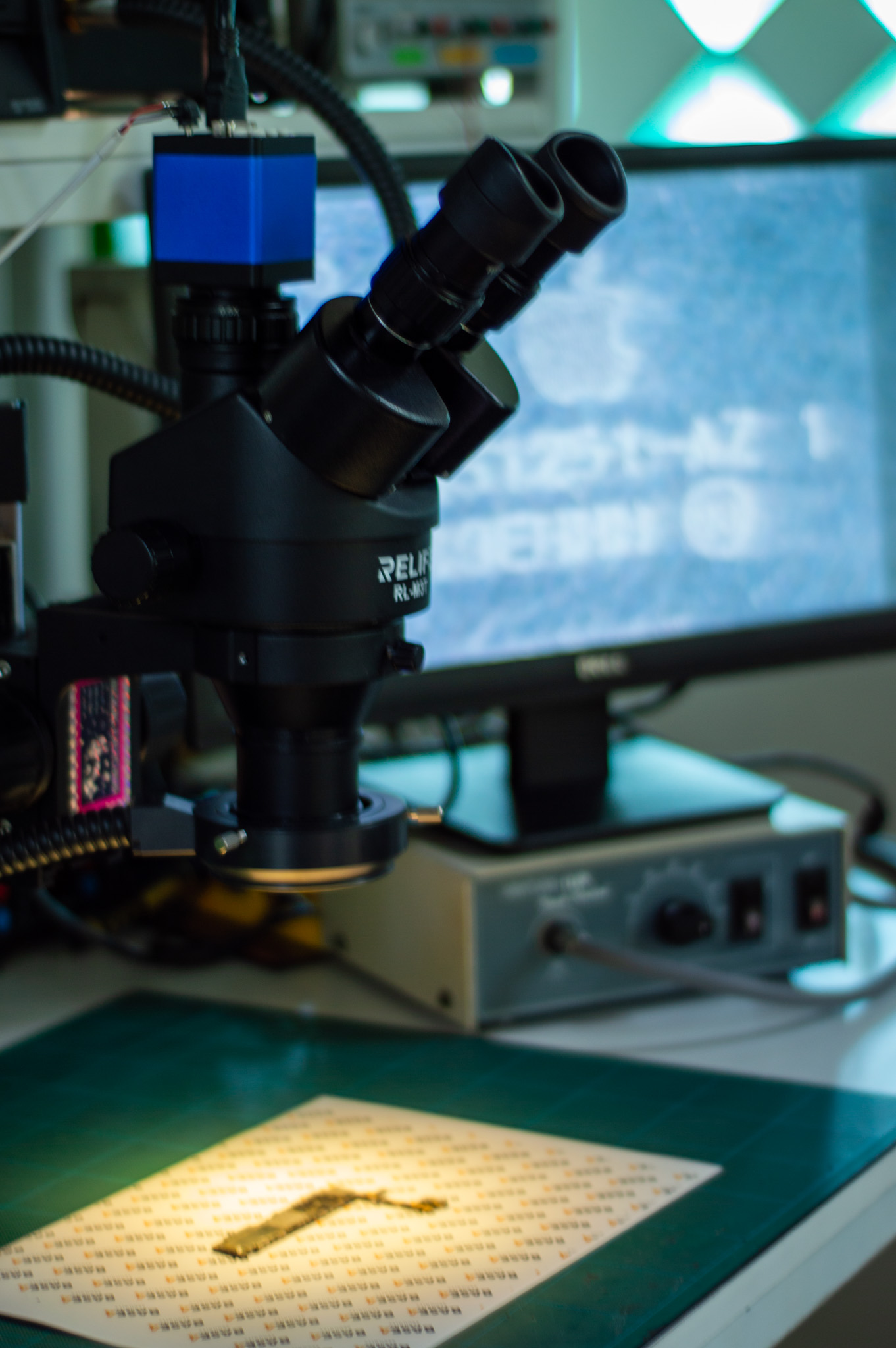

Graças a esse tipo de embalagem e a uma comunidade com o desejo de analisar o hardware no nível do silício para detectar modificações maliciosas ou falsificação de hardware, dirigindo a fabricação e modificação de ferramentas de custo acessível para tais atividades.

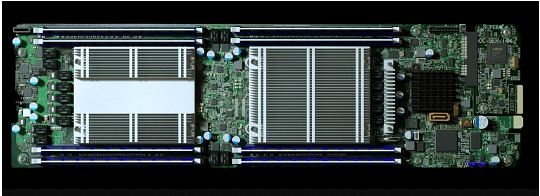

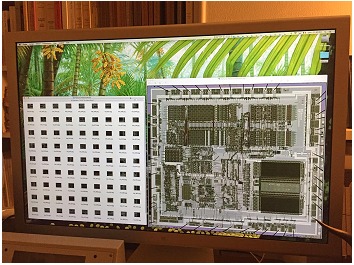

O sistema projeta uma matriz no IC e tira uma foto para cada posição atribuída pelo controlador que vimos anteriormente (essa foto é possível pela combinação de um microscópio biológico e uma câmera) então as fotos são adicionadas por software dando uma imagem de alta resolução do IC. No entanto, este exemplo ainda é destrutivo, já que as fotografias são tiradas em um dado sem sobre moldagem.

IRIS (infravermelho, in situ por Andrew "bunnie" Huang)

Mas neste post vamos combinar algumas das técnicas vistas anteriormente e acima de tudo vamos nos basear em uma técnica do engenheiro Andrew "bunnie" Huang. Que embora não tenha a resolução para análise em nível celular previamente resolvida com microscópios eletrônicos, apresenta resultados visíveis com microscópios convencionais, por isso foi escolhido para replicar.

Começamos com a imagem de um chip WLCSP em luz visível, montado em uma PCB disponível comercialmente (neste caso, uma placa-mãe do iPhone 6). A cena é inundada com luz halógena com quase todo o espectro visível ao olho humano. Como resultado, o chip parece prateado e opaco. Portanto, a microscopia de luz frontal não é adequada para inspeção in situ.

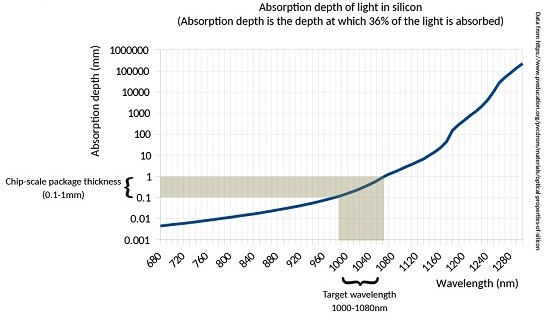

No entanto, um estudo óptico realizado no Silício nos diz que ele passa de opaco a transparente na faixa de comprimento de onda de 1000 nm a 1100 nm (faixa sombreada na ilustração abaixo). Acima de 1100 nm, é transparente como vidro; mas abaixo de 1000 nm torna-se rapidamente mais opaco.

Hipótese

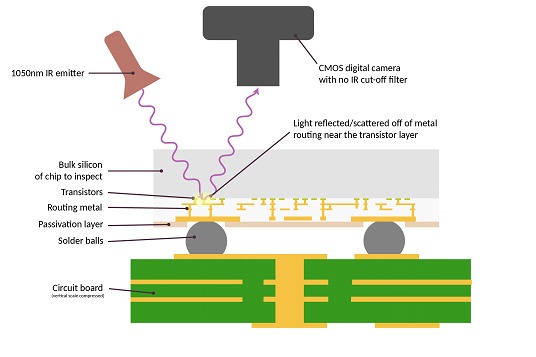

O esquema mostra a visão em corte transversal da configuração de inspeção IRIS. O IC como na vida real já está conectado a uma placa de circuito e estamos acendendo a parte de trás do chip de silício. A luz é refletida nas camadas de metal mais próximas dos transistores e é capturada em imagens com uma câmera. Conceitualmente, é bastante simples, mas existem algumas considerações a ter em conta:

Sensores CMOS padrão (aqueles usados por câmeras) retêm alguma sensibilidade ao infravermelho de ondas curtas. No entanto, o silício é transparente o suficiente para que luz suficiente passe através da camada de silício que forma a parte de trás de um pacote WLCSP para imagens de luz refletida. Mais especificamente, em 1000nm, um sensor CMOS pode ter 0,1x sua sensibilidade máxima, e um pedaço de silício de 0,3mm de espessura pode passar cerca de 10% da luz incidente - então, em geral, estamos falando de uma redução de ~100x na intensidade do sinal em comparação com as operações de luz visível. Embora essa redução não seja trivial, ela pode ser superada com a combinação de uma fonte de luz mais forte e um tempo de exposição mais longo (da ordem de alguns segundos).

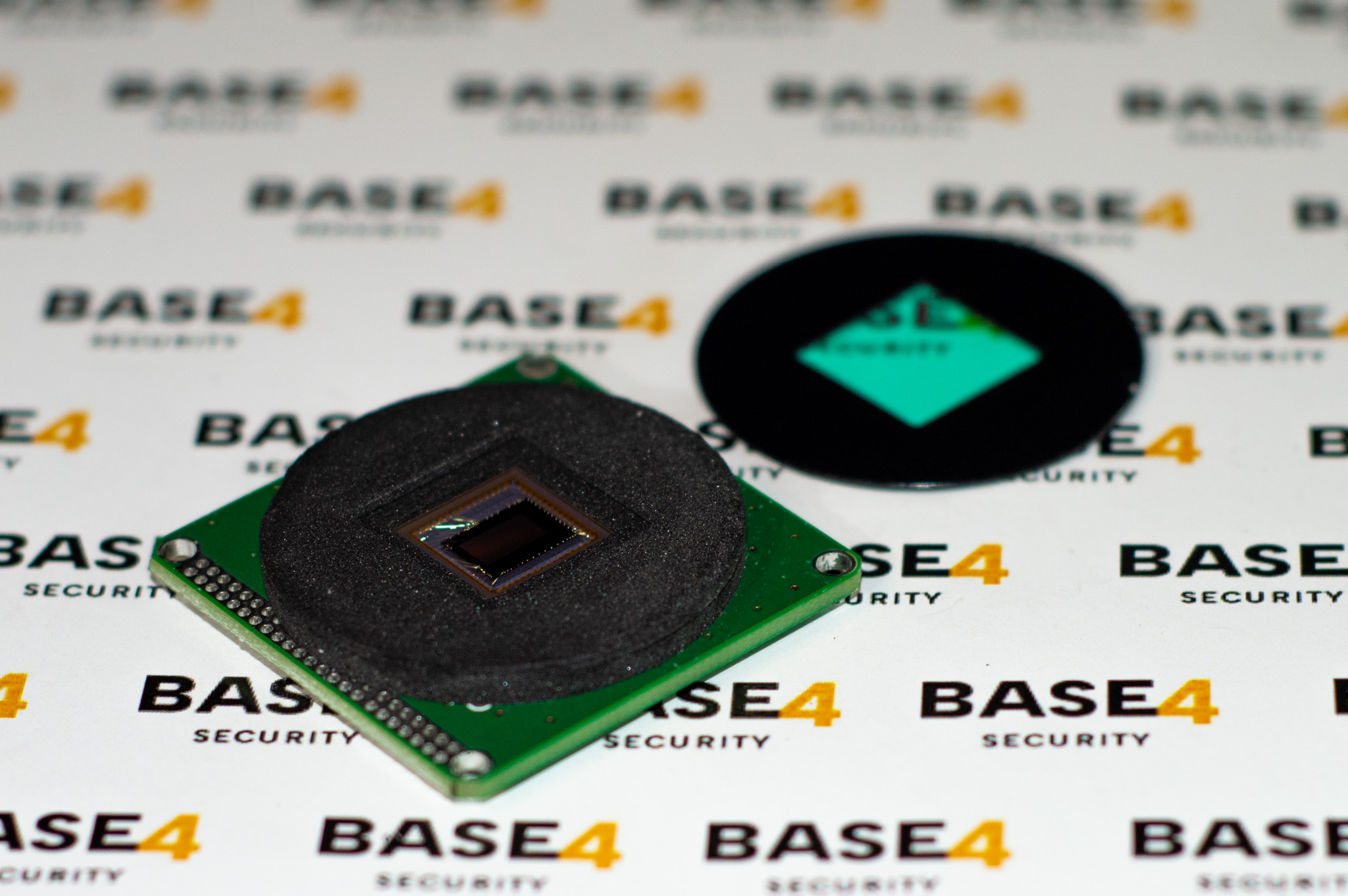

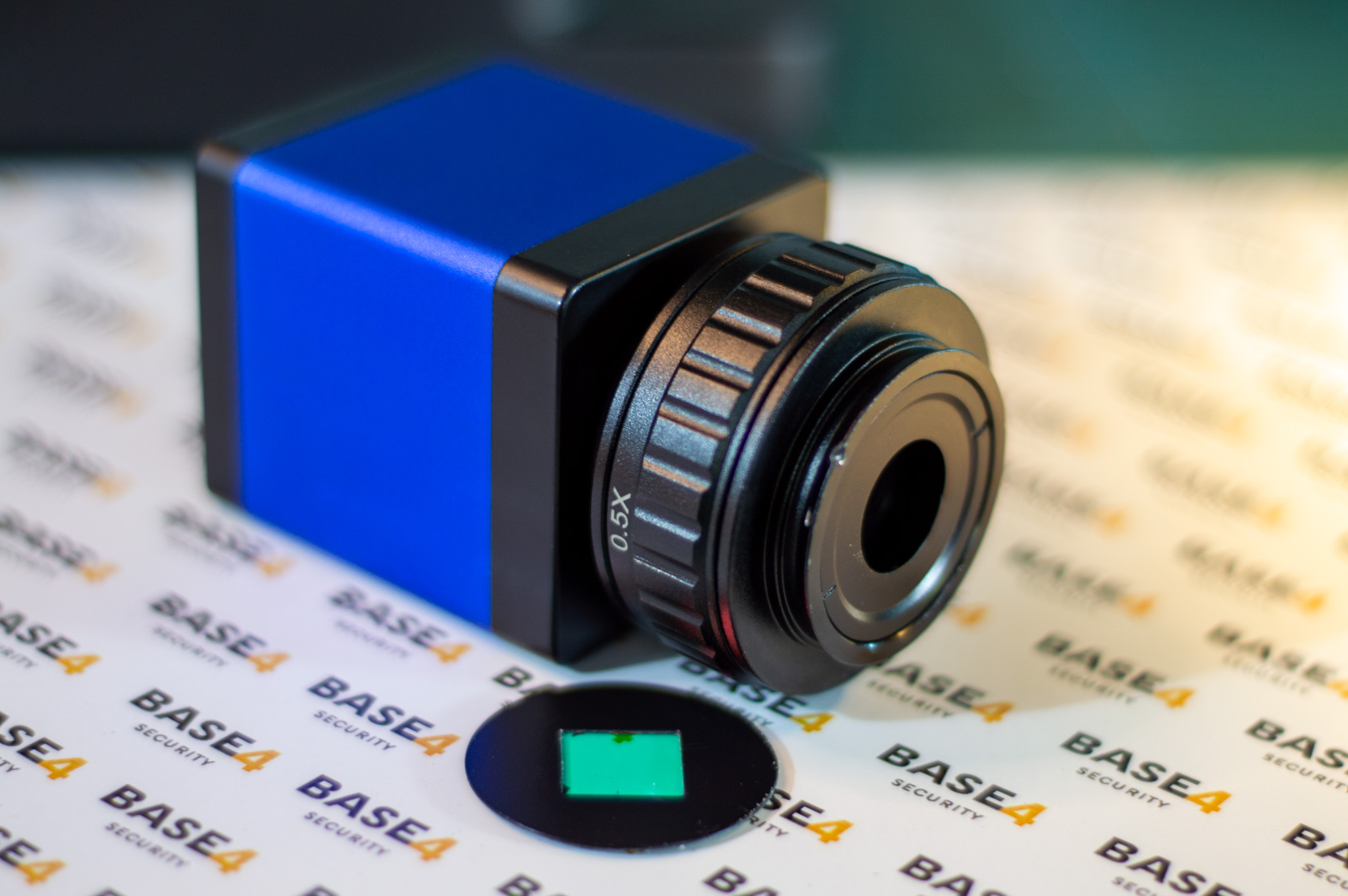

Mas podemos melhorar esses resultados se removermos o filtro de corte IR da câmera digital. Normalmente, a sensibilidade infravermelha extra dos sensores CMOS é considerada problemática, pois introduz artefatos de fidelidade de cores. Devido a esse excesso de sensibilidade, todas as câmeras digitais de consumo são despachadas com um filtro especial instalado que bloqueia qualquer entrada de luz infravermelha. Tirar esse filtro é uma técnica que se usa na Astrofotografia para poder captar nuvens de hidrogênio (deixo os links nas referências).

Em segundo lugar, precisamos de uma fonte de luz infravermelha. Lâmpadas incandescentes e luz solar natural contêm muita luz infravermelha, a configuração de demonstração atual usa um par de emissores de LED IF de 1070nm 100mA, mas infelizmente eles não estão disponíveis localmente, então testamos com lâmpadas infravermelhas destinadas a Cinesiologia e obtivemos os seguintes resultados.

Embora essas lâmpadas emitam em 1050-1070 nm, o excesso de outros comprimentos é acidentalmente refletido na superfície externa do chip e tende a inundar a luz refletida pelas camadas metálicas internas, o que faz com que a eficiência da câmera diminua muito e a imagem fique fraca, fraca e ruidosa.

Claro, poderíamos obter imagens de maior qualidade se investíssemos mais dinheiro em uma fonte, melhor ótica e uma câmera melhor. Mas teoricamente os resultados são suficientes.

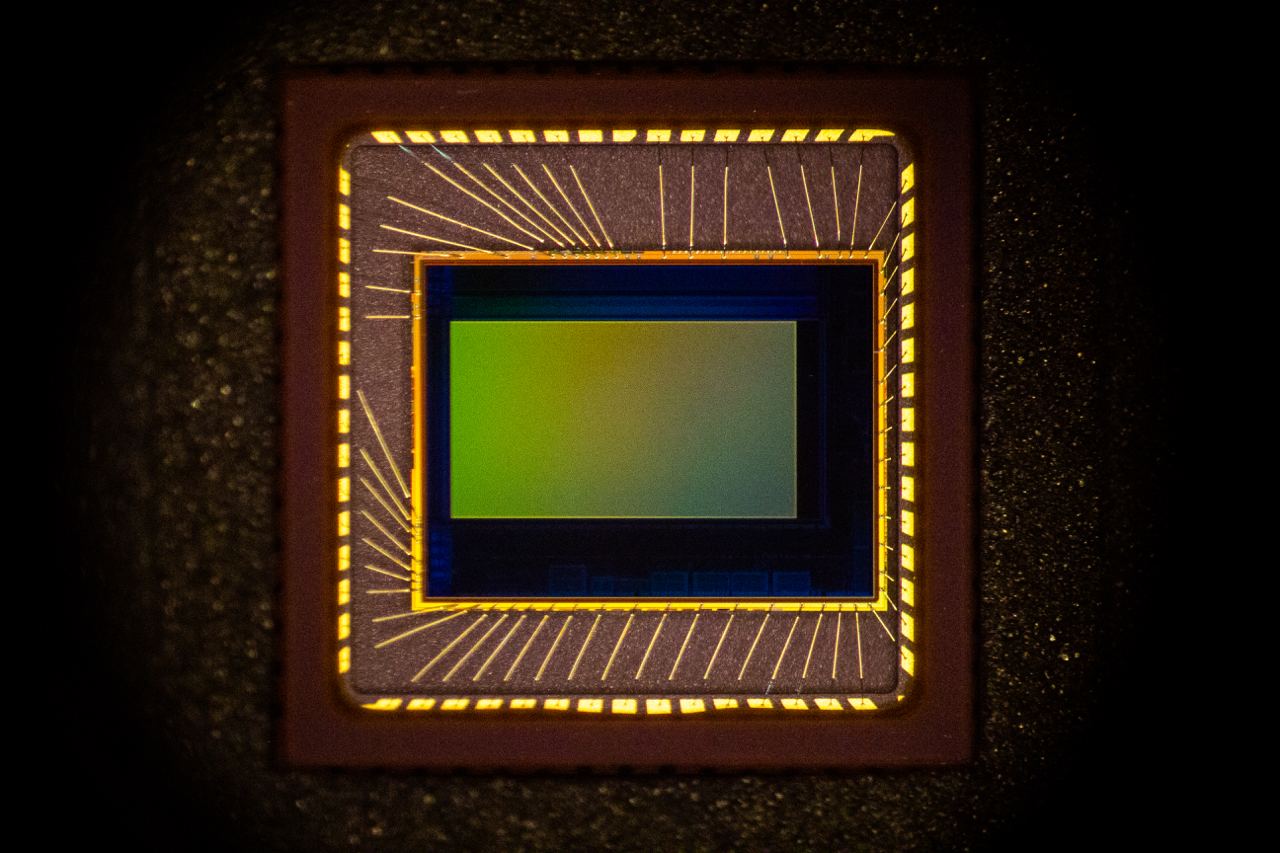

Abaixo estão as fotos tiradas pelo pesquisador original:

Conclusão

A inspeção IRIS revela a estrutura interna de um chip de silício. Felizmente, uma gama bastante ampla e popular de ICs já vem no formato WLCSP e FCBGA e expõe a parte traseira dos chips. Por si só, o IRIS não pode inspecionar os menores recursos de um chip; as portas lógicas individuais serão menores que um mícron de altura. Estes não podem ser resolvidos com comprimentos de onda infravermelhos e, como tal, não podem ser inspecionados diretamente, talvez combinando técnicas SEM isso possa serresolvido. Em suma, essa técnica é comparável a poder fazer um raio-X de uma mala em um aeroporto.

Quanto à possibilidade de detecção de cavalos de Tróia Mesmo com o SEM aprimorado, alterações maliciosas em chips chamadas “cavalos de Tróia de hardware” ainda podem ser muito difíceis de detectar, conforme demonstrado em “Stealthy Dopant-Level Hardware Trojans” de Georg T. Becker (2013). Este documento propõe que as modificações de dopagem seriam invisíveis para a maioria das formas de inspeção, incluindo SEM, pticrografia de raios-X e IRIS.

A boa notícia é que os ataques discutidos (Becker, 2013) são contra alvos que não foram totalmente protegidos contra trojans de hardware. Com uma quantidade razoável de proteção no nível do design, podemos aumentar o footprint lógico de um Trojan de hardware para algo grande o suficiente para ser detectado pelo IRIS. Felizmente, há um corpo de pesquisa sobre proteção de chips contra cavalos de Tróia, usando uma variedade de técnicas, incluindo bloqueio lógico, varreduras de autoteste integrado (BIST), impressão digital de atraso de caminho e métodos de auto-autenticação; todos esses tópicos podem ser encontrados no livro Autenticação de circuito integrado: Trojans de hardware e detecção de falsificações de Mohammad Tehranipoor, Hassan Salmani e Xuehui Zhang.

IRIS é um complemento necessário para os métodos de hardening no nível lógico, porque os métodos de hardening puramente lógicos são vulneráveis a desvios e emulação. Nesse cenário, um cavalo de Tróia de hardware inclui circuitos adicionais para evitar a detecção, testando automaticamente as respostas corretas, como um lobo disfarçado de ovelha que é vestido apenas quando um pastor está por perto. Como o IRIS pode restringir a estrutura da escala meso à macro, podemos descartar modificações de circuito de média a grande escala, dando-nos mais confiança nos resultados da verificação em microescala, conforme relatado pelos métodos de proteção de nível lógico.

Próximos Passos

IRIS é uma técnica promissora para melhorar a confiança no hardware. Com um pouco de premeditação e planejamento, os projetistas podem usar o IRIS em conjunto com o reforço lógico para obter confiança abrangente na integridade de um chip, desde a escala micro até a macro. Embora a técnica possa não ser adequada para todos os chips de um sistema, ela é adequada para parâmetros de chip que exigem alta segurança, como raízes de confiança e enclaves seguros.

Obviamente, o IRIS é mais eficaz quando combinado com o design de chip de código aberto. Em chips de código fechado, não sabemos o que estamos vendo ou o que estamos procurando; mas com chips de código aberto, podemos usar a fonte de design para aumentar os recursos do IRIS para identificar recursos de interesse.

Andrew "bunnie" Huang nos diz que durante o próximo ano, ele espera aprimorar a técnica principal do IRIS. Além de atualizar a óptica e adicionar controle digital do ângulo de azimute da luz incidente, isso deve desempenhar um papel importante na melhoria da usabilidade do IRIS. Recursos de subcomprimento de onda em um chip interagem com a luz incidente como um holograma. Ao modificar o azimute e o ângulo de iluminação, é provável que possamos obter ainda mais informações sobre a estrutura do circuito subjacente, mesmo que seja menor que o limite de difração do sistema. Pessoalmente, acredito que o rápido crescimento de uma comunidade, aliado a essas técnicas, nos aproxima de uma nova era de pesquisa em hardware que teria parecido fantasia anos atrás.

Referências

- Andrew ‘bunnie’ Huang “Infra-Red, In-Situ (IRIS) Inspection of Silicon”, Sutajio Ko-Usagi Pte Ltd, Singapore.

- “Red Team vs. Blue Team: A Real-World Hardware Trojan Detection Case Study Across Four Modern CMOS Technology Generations”

- Paul A. Karger, 2Lt, USAF, Roger R. Schell, Maj, USAF “Multics Security Evaluation: Vulnerability Analysis”, Deputy for Command and Management Systems (MCI), HQ Electronic Systems Division Hanscom AFB, MA 01730, 19 July 1972.

- Georg T. Becker1 , Francesco Regazzoni2 , Christof Paar1,3 , and Wayne P. Burleson1, “Stealthy Dopant-Level Hardware Trojans” , 1University of Massachusetts Amherst, USA 2TU Delft, The Netherlands and ALaRI - University of Lugano, Switzerland 3Horst G¨ortz Institut for IT-Security, Ruhr-Universit¨at Bochum, Germany.

- Shahin Tajik∗,1, Heiko Lohrke∗,2, Jean-Pierre Seifert1, and Christian Boit2 “On the Power of Optical Contactless Probing: Attacking Bitstream Encryption of FPGAs”1Security in Telecommunications, 2Semiconductor Devices Technische Universität Berlin, Germany

- Heiko Lohrke,1, Shahin Tajik,3,†, Thilo Krachenfels2,Christian Boit1, and Jean-Pierre Seifert2”Key Extraction Using Thermal Laser Stimulation”1Semiconductor Devices Group, 2Security in Telecommunications Group Technische Universität Berlin, Germany 3Florida Institute for Cybersecurity Research University of Florida, USA

- Ger de Graaf and Reinoud F. Wolffenbuttel. “Illumination Source Identification Using a CMOS Optical Microsystem”