Ideas, información y conocimientos compartidos por el equipo

de Investigación, Desarrollo e Innovación de BASE4 Security.

Técnicas de detección de troyanos en implementaciones de hardware

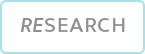

En 2018 nos sorprendió la noticia de que Amazon tres años atrás había comenzado a evaluar en silencio una startup llamada Elemental, que sería una adquisición estratégica para ayudar con la expansión de su servicio de transmisión de vídeo, conocido en la actualidad como Amazon Prime Video. Elemental había creado un software para comprimir archivos de vídeo masivos y formatearlos para diferentes dispositivos. Su tecnología había ayudado a transmitir los Juegos Olímpicos en línea, comunicarse con la Estación Espacial Internacional y canalizar imágenes de drones a la Agencia Central de Inteligencia. AWS, que supervisaba la posible adquisición, contrató a una empresa externa para analizar la seguridad de dicha empresa. En primer lugar se observó su producto principal: los costosos servidores que los clientes instalaban en sus redes para manejar la compresión de video. Estos servidores fueron ensamblados para Elemental por Supermicro Computer Inc. que es uno de los mayores proveedores mundiales de placas base para servidores.

Pero durante la investigación encontraron un pequeño microchip, que no formaba parte del diseño original de las PCB. Amazon informó el descubrimiento a las autoridades estadounidenses, enviando un estremecimiento a través de la comunidad de inteligencia ya que los servidores de Elemental se pueden encontrar en los centros de datos del Departamento de Defensa, las operaciones de drones de la CIA y las redes a bordo de buques de guerra de la Armada. Elemental era tan solo uno de los cientos de clientes de Supermicro.

Los investigadores determinaron que el microchip permitía a atacantes crear una puerta sigilosa en cualquier red que incluyera los servidores alterados. Se presupone que los chips habían sido instalados en fábricas administradas por subcontratistas de fabricación en China.

Este tipo de ataque fue algo más grave que los incidentes basados en software que estamos acostumbrados a ver. Los hacks de hardware son más difíciles de lograr y potencialmente más devastadores, permitiendo a largo plazo accesos a cualquier tipo de empresa que implemente estas soluciones.

Hay dos formas para alterar el interior de un equipo informático. Uno, conocido como interdicción, consiste en manipular dispositivos que se encuentran en tránsito desde el fabricante al cliente. Agencias de espionaje de EE. UU. se ven favorecidas con este método, según documentos filtrados por el ex contratista de la NSA Edward Snowden.

El otro método implica modificaciones desde la fabricación. Un país en particular tiene la ventaja de ejecutar este tipo de ataque: China, que según algunas estimaciones fabrica el 75% de los teléfonos móviles del mundo y el 90% de las PCs. Aun así, lograr un ataque de “siembra” significa desarrollar una comprensión profunda del diseño de un producto, manipularlo sin afectar sus funciones o componentes y hacerlo dentro de la fábrica en un tiempo récord, y no menor asegurarse que estos dispositivos pasen desapercibidos por una gran cadena de logística global hasta llegar a la ubicación deseada.

Finalmente, estos investigadores descubrieron que eventualmente este ataque de “siembra” afectó a casi 30 empresas, incluido un banco importante, contratistas gubernamentales y la empresa más valiosa del mundo, Apple. Apple era un importante cliente de Supermicro y había planeado pedir más de 30,000 de sus servidores en dos años para una nueva red global de centros de datos. Tres expertos de alto rango en Apple dicen que en el verano de 2015, también se encontraron chips maliciosos en las placas base de Supermicro. Luego Apple cortó los lazos con Supermicro al año siguiente, pero describieron sus causas a razones no relacionadas con este hecho.

El gobierno chino no abordó directamente las preguntas sobre la manipulación de los servidores Supermicro, emitiendo una declaración que decía, en parte, “La seguridad de la cadena de suministro en el ciberespacio es un tema de interés común, y China también es una víctima.” El FBI y la Oficina del Director de Inteligencia Nacional, en representación de la CIA y la NSA, declinaron hacer comentarios.Hoy, Supermicro vende más placas base de servidor que casi cualquier otra empresa en el mundo. También domina el mercado para PCBs utilizadas en computadoras especiales, desde máquinas de resonancia magnética hasta sistemas de armas. Sus placas base se pueden encontrar en configuraciones de servidores hechas a medida en bancos, fondos de cobertura, proveedores de computación en la nube y servicios de alojamiento web, entre otros lugares. Supermicro tiene instalaciones de ensamblaje en California, los Países Bajos y Taiwán, pero sus placas base son casi todas fabricadas por contratistas en China.

Actualidad

Si bien a la fecha de escribir este post ya casi pasó una década de la investigación que mencionamos anteriormente y más de medio siglo desde que se utilizó por primera vez el término troyano o mejor dicho, caballo de Troya en un informe de la Fuerza Aérea de EEUU en titulado “Multics Security Evaluation: Vulnerability Analysis” que mencionaba como pequeños bloques de código podrían afectar el hardware de sistemas de control de accesos haciéndose pasar por algo que no eran, en la actualidad, detectar troyanos en hardware se volvió una dificultad, ya que estos ya no solo se encuentran en un “microchip” extra agregados a un PCB, sino que los pequeños transistores que componen al “microchip malicioso” podrían estar incluidos en el troquel de silicio de los procesadores e integrados objetivos.

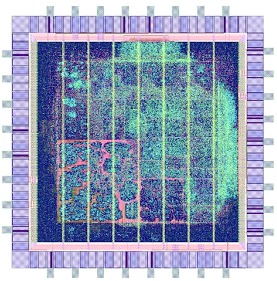

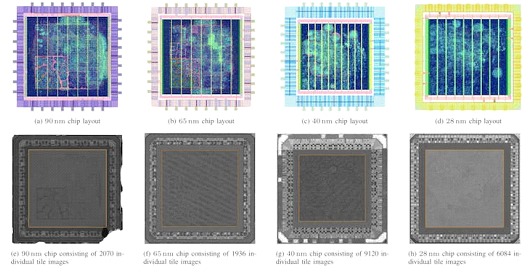

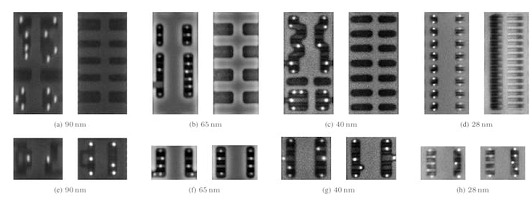

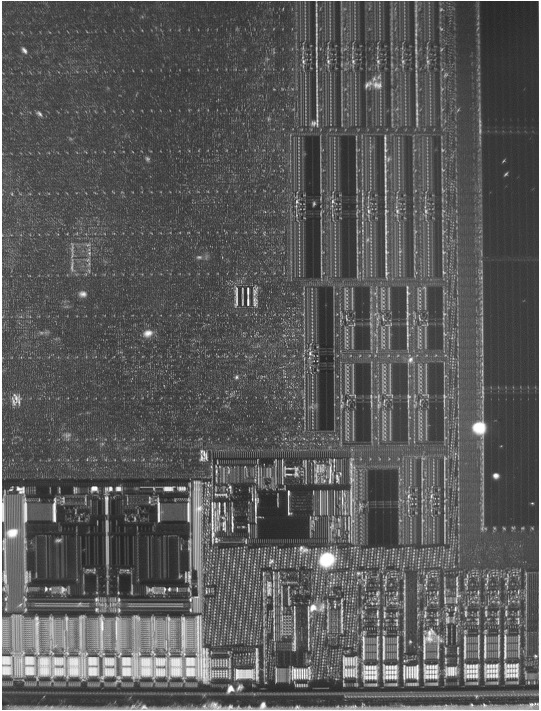

Utilizando miles de imágenes de microscopio electrónico y comparándolas con el diseño original del chip, un grupo de investigadores de la Universidad Ruhr Bochum y el Instituto Max Planck de Seguridad y Privacidad (MPI-SP) han ideado un enfoque para analizar fotos de troqueles de microchips para revelar los ataques de troyanos en nuestro hardware y no solo están teniendo buenos resultados sino que están lanzando sus imágenes y algoritmos para que cualquier investigador independiente lo intenten.

"Es concebible que se puedan insertar pequeños cambios en los diseños de las fábricas poco antes de la producción que podrían anular la seguridad de los “chips", dice Steffen Becker, coautor del artículo que detalla el trabajo. "En casos extremos, tales troyanos de hardware podrían permitir que un atacante paralice partes de la infraestructura de telecomunicaciones con solo presionar un botón."

Al observar los chips construidos en procesos de 28 nm, 40 nm, 65 nm y 90 nm, el equipo se dedicó a automatizar el proceso de inspección de dichos chips. Utilizando diseños creados por Thorben Moos, descubrieron una forma de probar su enfoque: "Comparar las imágenes de chips y los planes de construcción resultó ser un gran desafío, porque primero tuvimos que superponer con precisión los datos", dice el primer autor Endres Puschner. "En el chip más pequeño, que tiene un tamaño de 28 nanómetros, una sola mota de polvo o un cabello puede oscurecer una fila completa de celdas estándar."

A pesar de estos desafíos, el algoritmo de análisis se mostró prometedor, detectando automáticamente 37 de las 40 modificaciones realizadas para la prueba incluyendo las realizadas en los chips construidos en procesos entre 40 nm y 90 nm. El algoritmo, sin duda, arrojó 500 falsos positivos — pero, dice Puschner, "con más de 1.5 millones de celdas estándar examinadas, esta es una muy buena tasa."

Si desea realizar sus propias pruebas al final de este post no olvide ver las referencias en donde se podrá encontrar el documento del equipo y el código utilizado que fue publicado en GitHub bajo la licencia permisiva del MIT.

Técnicas Actuales

Hoy en día hay muchas opciones para inspeccionar la construcción de chips; sin embargo, todas estas técnicas tienen un problema “Tiempo de verificación vs Tiempo de uso”. En otras palabras, ninguna de estas técnicas es in situ. Deben realizarse en muestras de chips que sean meramente representativos del dispositivo, o deben hacerse en instalaciones remotas de modo que la muestra pase por las manos de muchos extraños antes de regresar a su dueño. La microscopía electrónica de escaneo (SEM), ejemplificada anteriormente, es un método popular para inspeccionar chips. La técnica puede producir imágenes altamente detalladas de incluso los últimos transistores a escala nanométrica. Sin embargo, la técnica es destructiva: solo puede sondear la superficie de un material. Para obtener imágenes de los transistores, uno debe eliminar mediante técnicas como decapping las capas superiores del encapsulado hasta llegar al metal. Por lo tanto, la técnica no es adecuada para una inspección in situ.

Los Rayos X al margen de contar con el instrumental y las protecciones correspondientes, no son destructivos y son capaces de hacer una inspección in situ. Sin embargo, el silicio es casi transparente a los tipos de rayos X utilizados normalmente, se puede llegar a utilizar para identificar el tamaño de las secciones y la posición de los hilos de oro que viajan desde los pads hasta el troquel de silicio, pero no puede darnos información sobre el patrón de los transistores.

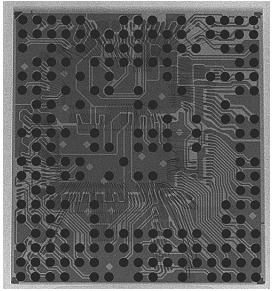

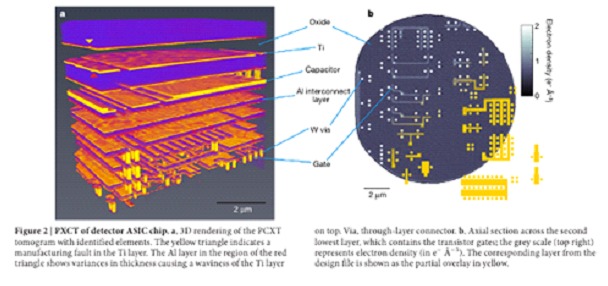

Por otro lado, la tipografía de rayos X es una técnica que utiliza rayos X de alta energía que pueden establecer de manera no destructiva el patrón de transistores en un chip. La siguiente imagen es un ejemplo de una imagen 3D de alta resolución generada por la técnica, como se revela en el paper “High-resolution non-destructive three-dimensional imaging of integrated circuits"

Es una técnica muy poderosa, pero desafortunadamente requiere una fuente de luz del tamaño de un edificio, como la Fuente de luz suiza (SLS) (edificio en forma de rosquilla en la imagen), de los cuales hay pocos en el mundo. Si bien es un método poderoso, no es práctico inspeccionar cada dispositivo y menos de un usuario final.

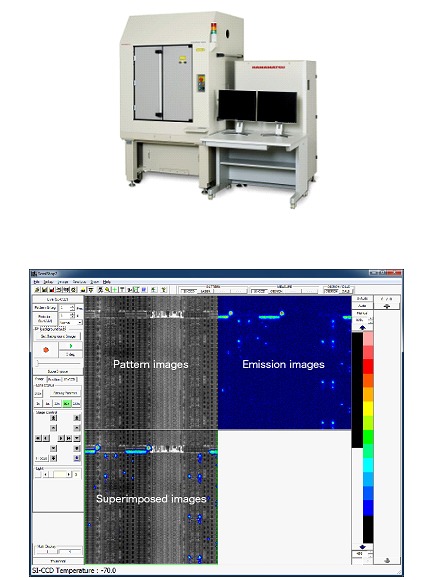

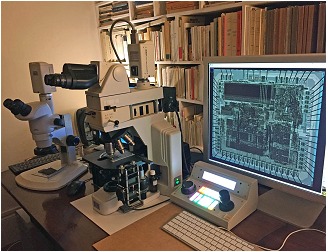

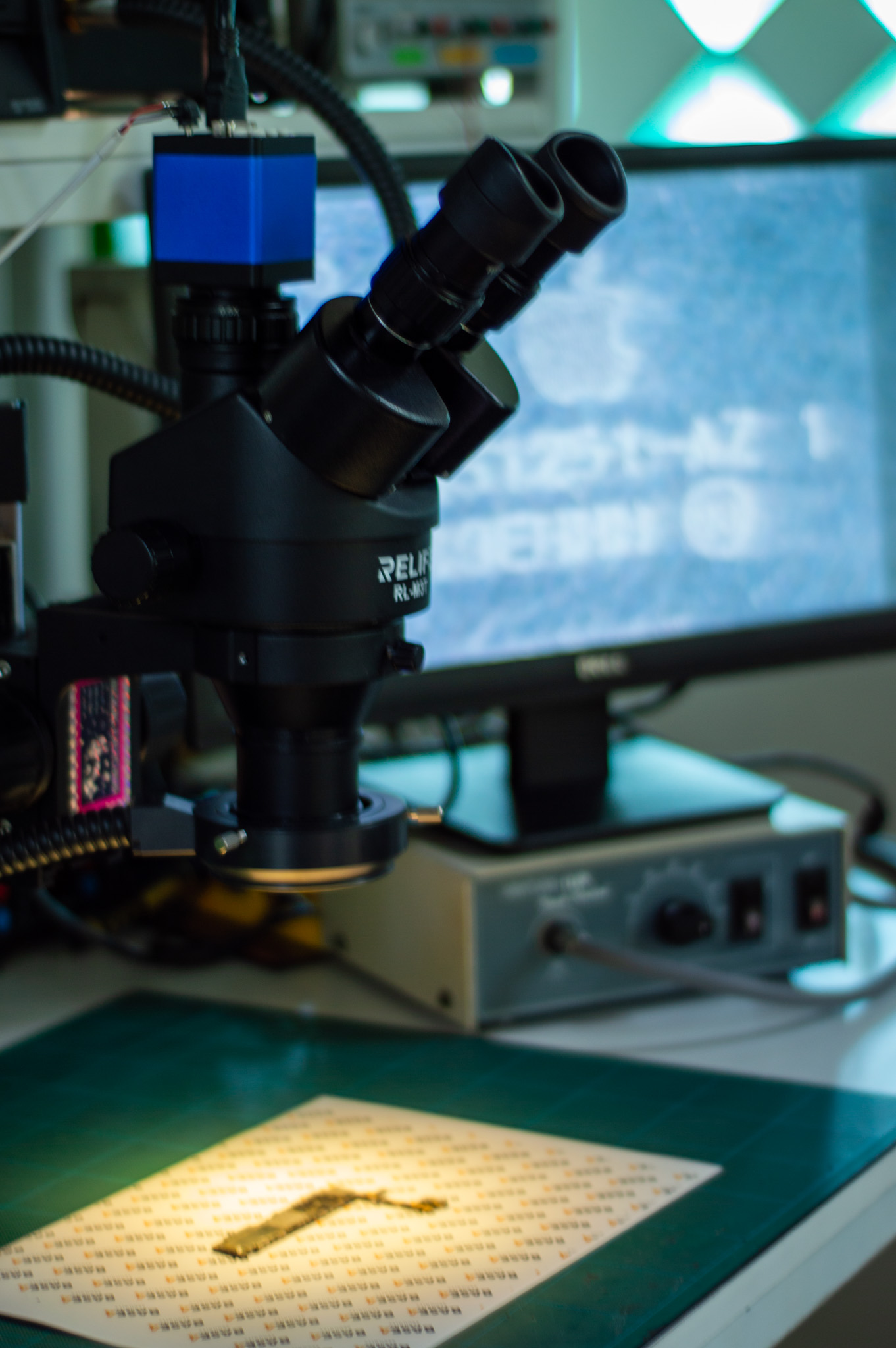

Algunas empresas desarrollaron “Laboratorios Portátiles” como es el caso de Hamamatsu con su Microscopio de emisión PHEMOS-1000 que lo describen como un microscopio de alta resolución que señala las ubicaciones de falla en dispositivos semiconductores al detectar las débiles emisiones de luz y las emisiones de calor causadas por defectos en dispositivos semiconductores. Se le puede instalar un sistema de escaneo láser opcional y permite adquirir imágenes de patrones de alta resolución.

Esta última parece una solución ideal, pero lamentablemente es un equipo que junto a sus accesorios alcanza un valor de U$D1M por lo que se restringe bastante al público.

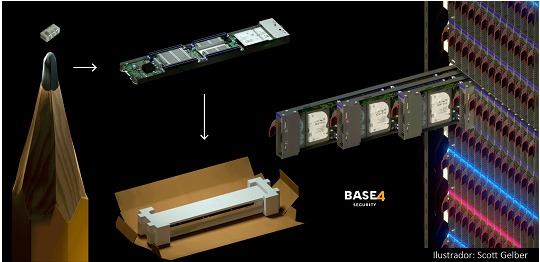

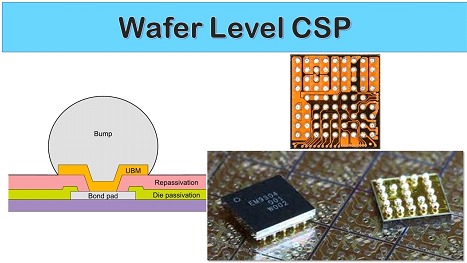

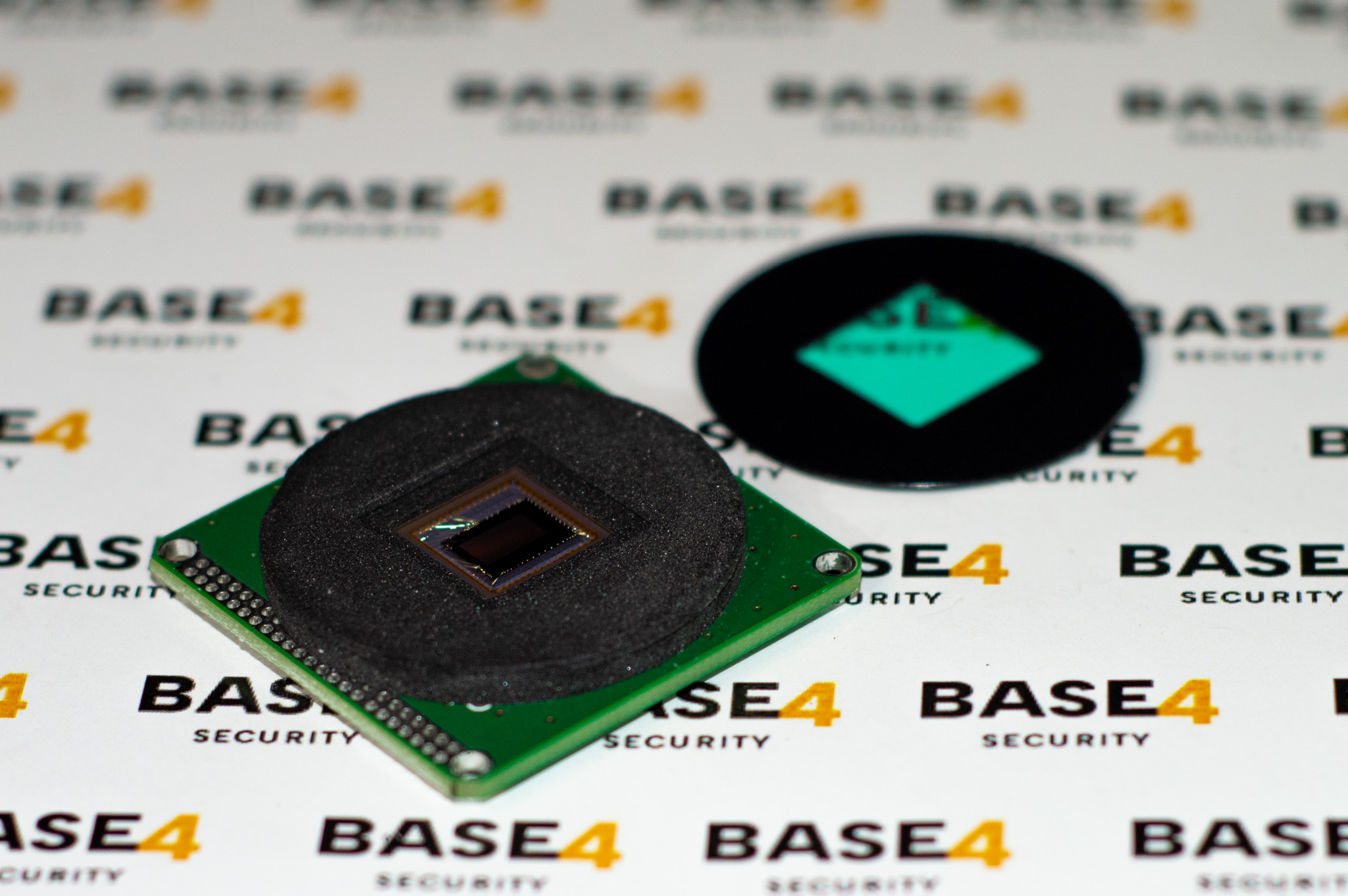

Afortunadamente, en el mundo de los chips, se ha vuelto cada vez más popular encapsular chips sin plástico sobremoldeado. La desventaja de exponer los delicados chips de silicio a posibles abusos mecánicos se ve compensada por un rendimiento térmico mejorado, mejores características eléctricas y, por lo general, menores costos en comparación con el sobremoldeo. Debido a sus ventajas convincentes, este estilo de empaque es omnipresente en los dispositivos móviles. A este tipo de encapsulado se lo conoce normalmente como WLCSP o Wafer-level packaging.

Gracias a este tipo de encapsulados y a una comunidad con el deseo de analizar hardware a nivel de silicio para detectar modificaciones maliciosas o hardware falsificado se están impulsando la fabricación y modificación de herramientas de costos accesibles para dichas actividades.

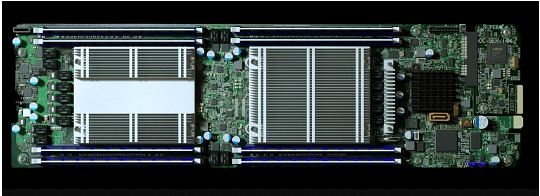

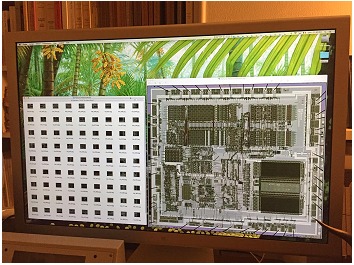

El sistema diseña una matriz sobre el ic y toma una fotografía por cada posición asignada por el controlador que vimos anteriormente (esta fotografía es posible por la combinación de un microscopio biológico y una cámara) luego las fotografías se suman mediante un software otorgando una imagen de alta resolución del ic. Sin embargo este ejemplo sigue siendo destructivo, ya que las fotografías están tomadas sobre un troquel sin sobre moldeo.

IRIS (Infrarrojo, In Situ by Andrew "bunnie" Huang)

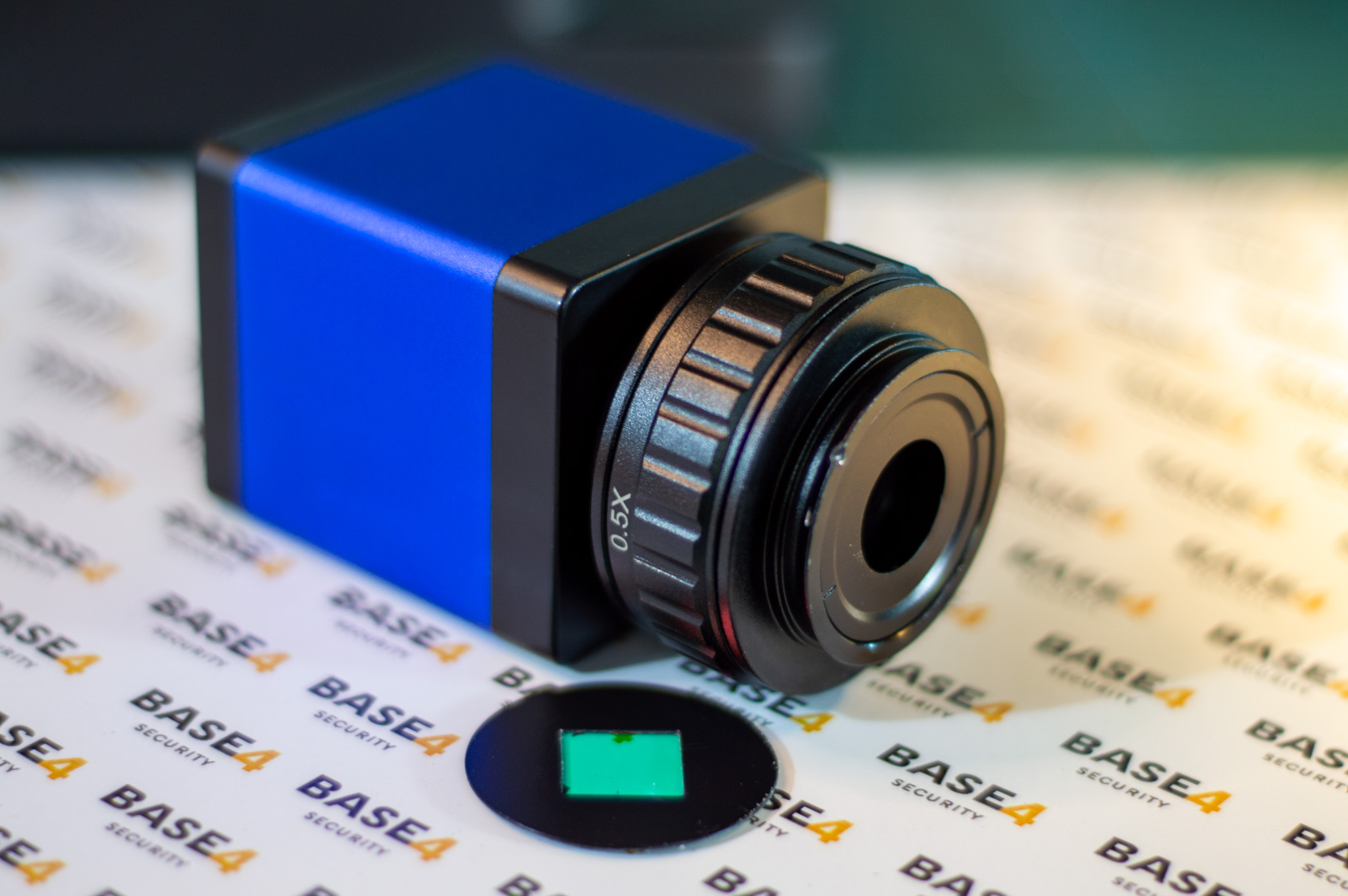

Pero en este post vamos a combinar alguna de las técnicas vistas anteriormente y sobre todo nos vamos a basar en una técnica del ingeniero Andrew "bunnie" Huang. Que si bien carece de la resolución para el análisis a nivel celular solucionado anteriormente con microscopios electrónicos arroja resultados visibles con microscopios convencionales por eso fue la elegida para replicar.

Comenzamos con una imagen de un chip WLCSP en luz visible, ensamblado en una PCB ya comercializada (en este caso, una placa base de un iPhone 6). La escena se inunda con una luz halógena con casi todo el espectro visible por el ojo humano. Como resultado, el chip parece plateado y opaco. Por lo tanto, la microscopía óptica frontal no es adecuada para la inspección in situ.

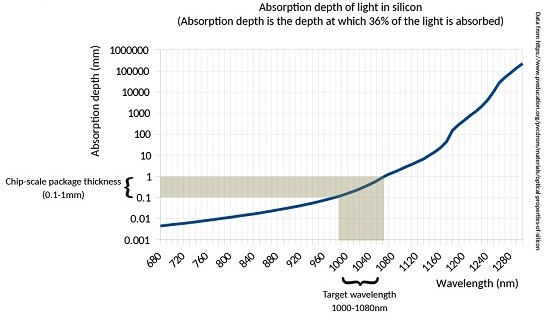

Sin embargo un estudio óptico realizado sobre el Silicio nos adelanta que este pasa de ser opaco a transparente en el rango de longitud de onda de 1000 nm a 1100 nm (banda sombreada en la ilustración a continuación). Por encima de 1100 nm, es tan transparente como un vidrio; pero por debajo de 1000 nm, rápidamente se vuelve más opaco.

Hipótesis

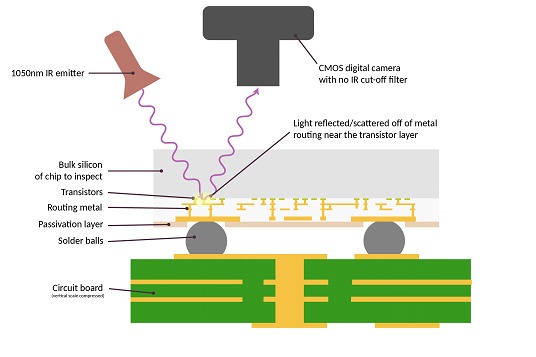

En el esquema se plantea la sección de vista transversal de la configuración de inspección IRIS. El IC al igual que en la vida real ya está unido a una placa de circuito y estamos iluminando la parte posterior del chip de silicio. La luz se refleja en las capas de metal más cercanas a los transistores, y se toma en imágenes con una cámara. Conceptualmente, es bastante sencillo, pero hay que tener en cuenta algunas consideraciones:

Los sensores CMOS estándar (los que utilizan las cámaras) retienen cierta sensibilidad al infrarrojo de onda corta. Sin embargo, el silicio es lo suficientemente transparente como para que pase suficiente luz a través de la capa de silicio a granel que forma la parte posterior de un paquete WLCSP para realizar imágenes de luz reflejada. Más concretamente, a 1000 nm, un sensor CMOS podría tener 0.1x su sensibilidad máxima, y una pieza de silicio de 0.3 mm de espesor puede pasar aproximadamente un 10% de la luz incidente –, por lo que en general estamos hablando de una reducción ~ 100x en la intensidad de la señal en comparación con las operaciones de luz visible. Si bien esta reducción no es trivial, se puede superar con una combinación de una fuente de luz más intensa y un tiempo de exposición más largo (del orden de varios segundos).

Pero podemos mejorar estos resultados si retiramos el filtro de corte IR de la cámara digital. Normalmente, la sensibilidad infrarroja adicional de los sensores CMOS se considera problemática, ya que introduce artefactos de fidelidad de color. Debido a este exceso de sensibilidad, todas las cámaras digitales de consumo se envían con un filtro especial instalado que bloquea cualquier luz IR entrante. Retirar ese filtro es una técnica que se utiliza en Astrofotografía para poder capturar las nubes de hidrógeno(en referencia dejo los links).

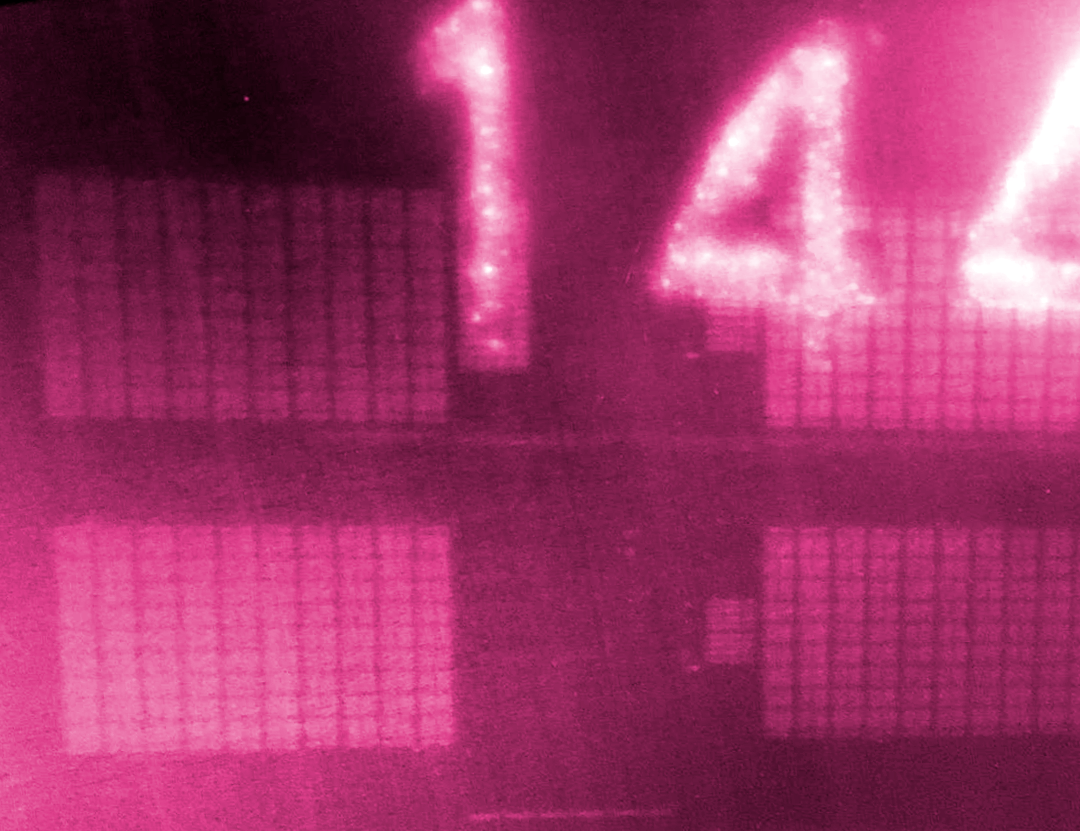

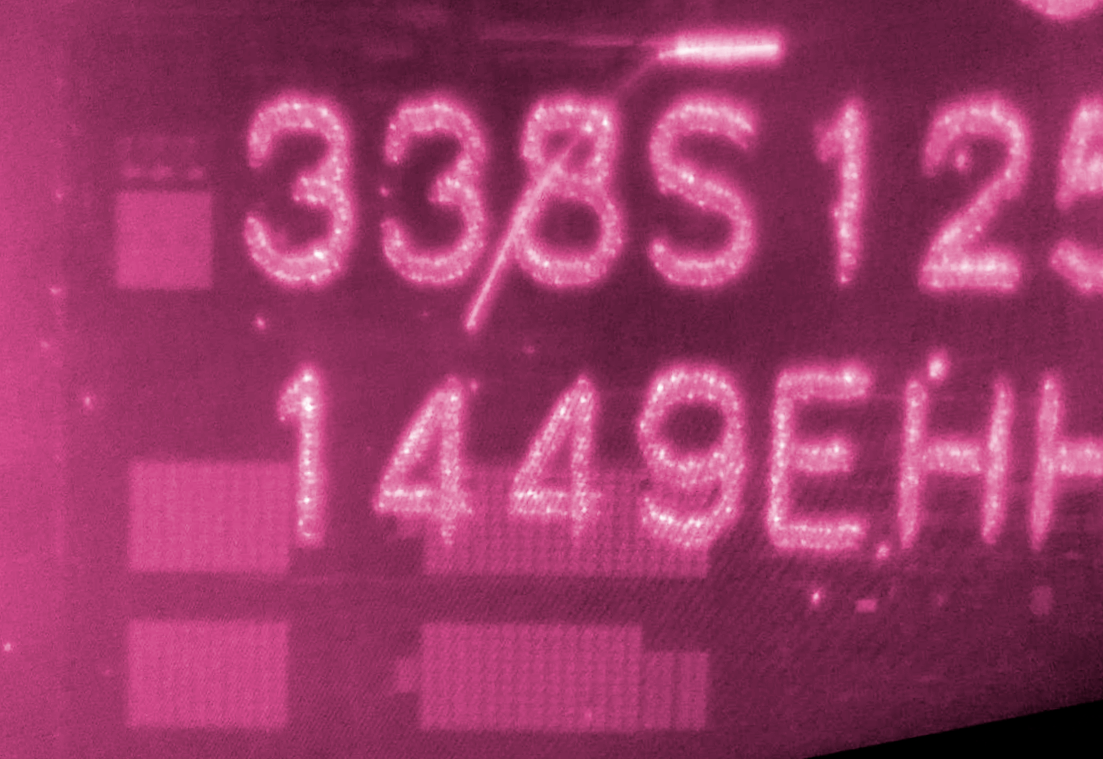

En segundo lugar, necesitamos una fuente de luz IR. Las bombillas incandescentes y la luz solar natural contienen mucha luz IR, la configuración de la demostración actual utiliza un par de emisores LED IF de 1070 nm y 100 mA, pero lamentablemente no se consiguen en el mercado local, por lo que realizamos las pruebas con lámparas IR destinadas a Kinesiologia y obtuvimos los siguientes resultados.

Si bien estas lámparas emiten en 1050-1070 nm el exceso de otras longitudes se refleja accidentalmente en la superficie externa del chip y tiende a inundar la luz reflejada por las capas metálicas internas por lo que la eficiencia de la cámara disminuye demasiado y la imagen es demasiado débil y ruidosa.

Por supuesto, podríamos obtener imágenes de mayor calidad si invertimos más dinero en una fuente, mejor óptica y una mejor cámara. Pero a modo teórico los resultados son suficientes.

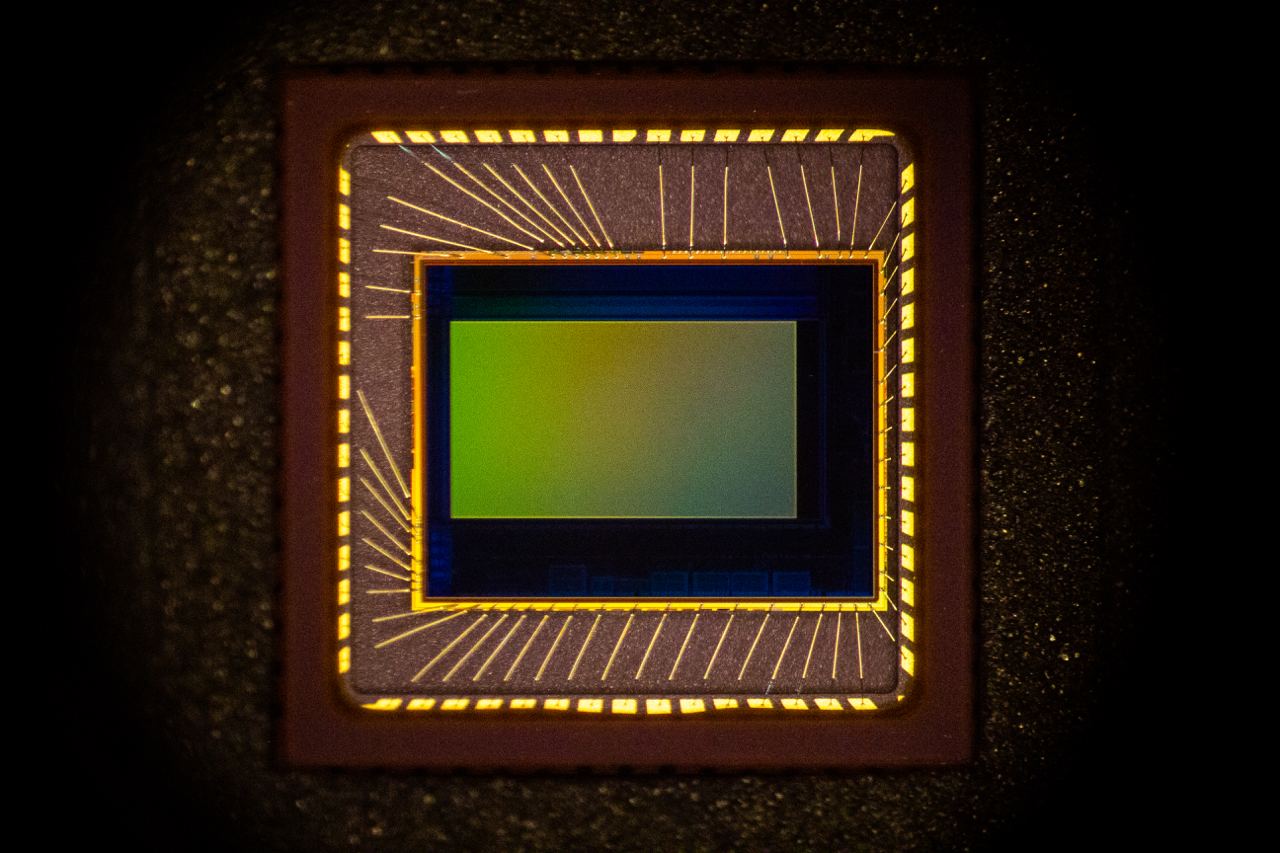

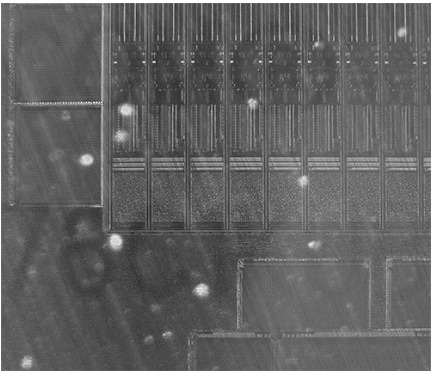

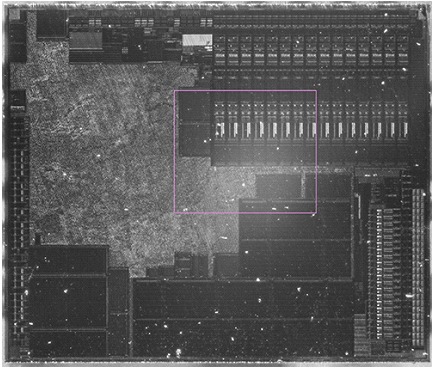

A continuación fotografías tomadas por el investigador original:

Conclusión

La inspección IRIS revela la estructura interna de un chip de silicio. Afortunadamente, una gama bastante amplia y popular de ics ya vienen en formato WLCSP y FCBGA y expone la parte posterior de los chips. Por sí misma IRIS no puede inspeccionar las características más pequeñas de un chip, las puertas lógicas individuales, serán más pequeñas que una micra de alto. Estos no se pueden resolver con longitudes de onda infrarrojas y, como tales, no se pueden inspeccionar directamente quizás combinando técnicas SEM, esto se resuelva. En resumen esta técnica es comparable a poder radiografiar una maleta en un aeropuerto.

Respecto a si es posible detectar troyanos Incluso con la mejora SEM, los cambios maliciosos en los chips denominados “troyanos de hardware” pueden seguir siendo realmente difíciles de detectar, como se demuestra en “Stealthy Dopant-Level Hardware Trojans” por Georg T. Becker(2013). Este Paper propone que las modificaciones de dopaje serían invisibles para la mayoría de las formas de inspección, incluidos SEM, X-Ray ptychography e IRIS.

La buena noticia es que los ataques discutidos (Becker, 2013) están en contra de objetivos en los que no se ha hecho hardening por completo contra los troyanos de hardware. Con una cantidad razonable de hardening a nivel de diseño, podemos aumentar la huella lógica de un troyano de hardware en algo lo suficientemente grande como para ser detectado con IRIS. Afortunadamente, existe un cuerpo de investigación sobre hardening de los chips contra los troyanos, utilizando una variedad de técnicas que incluyen bloqueo lógico, autoevaluación incorporada (BIST) escaneos, huellas digitales de retraso de trayectoria, y métodos de auto autenticación; todos estos temas se puede encontrar en el libro Integrated Circuit Authentication: Hardware Trojans and Counterfeit Detection de Mohammad Tehranipoor, Hassan Salmani, y Xuehui Zhang.

IRIS es un complemento necesario para los métodos de hardening a nivel lógico, porque los métodos de solo lógica son vulnerables a las derivaciones y la emulación. En este escenario, un troyano de hardware incluye circuitos adicionales para evadir la detección mediante pruebas automáticas con respuestas correctas, como un lobo que lleva el disfraz de una oveja que se pone solo cuando un pastor está cerca. Dado que IRIS puede restringir la estructura de escala meso a macro, podemos descartar modificaciones de circuito de escala media a grande, dándonos más confianza en los resultados de la verificación a microescala según lo informado por los métodos de endurecimiento a nivel lógico.

Próximos pasos

IRIS es una técnica prometedora para mejorar la confianza en el hardware. Con un poco de previsión y planificación, los diseñadores pueden usar IRIS junto con el hardening lógico para ganar una confianza integral en la integridad de un chip desde la micro a la macroescala. Si bien la técnica puede no ser adecuada para cada chip en un sistema, se adapta cómodamente a los parámetros de los chips que requieren una alta seguridad, como raíces de confianza y enclaves seguros.

Por supuesto, IRIS es más efectivo cuando se combina con el diseño de chip de código abierto. En chips de código cerrado, no sabemos qué estamos viendo o qué estamos buscando; pero con chips de código abierto podemos usar la fuente de diseño para aumentar las capacidades de IRIS para identificar características de interés.

Andrew "bunnie" Huang nos cuenta que durante el próximo año, espera mejorar la técnica central de IRIS. Además de actualizar la óptica y agregar un control digital del ángulo y el acimut de la luz incidente esto debería desempeñar un papel importante en la mejora de la utilidad de IRIS. Las características de sub-longitud de onda en un chip interactúan con la luz incidente como un holograma. Al modificar el acimut y el ángulo de iluminación, es probable que podamos obtener aún más información sobre la estructura de los circuitos subyacentes, incluso si son más pequeños que el límite de difracción del sistema. Personalmente, creo que el rápido crecimiento de una comunidad y junto a estas técnicas nos acercan a una nueva era de investigación sobre el hardware casi de fantasía si la pensamos años atrás.

Referencias

- Andrew ‘bunnie’ Huang “Infra-Red, In-Situ (IRIS) Inspection of Silicon”, Sutajio Ko-Usagi Pte Ltd, Singapore.

- “Red Team vs. Blue Team: A Real-World Hardware Trojan Detection Case Study Across Four Modern CMOS Technology Generations”

- Paul A. Karger, 2Lt, USAF, Roger R. Schell, Maj, USAF “Multics Security Evaluation: Vulnerability Analysis”, Deputy for Command and Management Systems (MCI), HQ Electronic Systems Division Hanscom AFB, MA 01730, 19 July 1972.

- Georg T. Becker1 , Francesco Regazzoni2 , Christof Paar1,3 , and Wayne P. Burleson1, “Stealthy Dopant-Level Hardware Trojans” , 1University of Massachusetts Amherst, USA 2TU Delft, The Netherlands and ALaRI - University of Lugano, Switzerland 3Horst G¨ortz Institut for IT-Security, Ruhr-Universit¨at Bochum, Germany.

- Shahin Tajik∗,1, Heiko Lohrke∗,2, Jean-Pierre Seifert1, and Christian Boit2 “On the Power of Optical Contactless Probing: Attacking Bitstream Encryption of FPGAs”1Security in Telecommunications, 2Semiconductor Devices Technische Universität Berlin, Germany

- Heiko Lohrke,1, Shahin Tajik,3,†, Thilo Krachenfels2,Christian Boit1, and Jean-Pierre Seifert2”Key Extraction Using Thermal Laser Stimulation”1Semiconductor Devices Group, 2Security in Telecommunications Group Technische Universität Berlin, Germany 3Florida Institute for Cybersecurity Research University of Florida, USA

- Ger de Graaf and Reinoud F. Wolffenbuttel. “Illumination Source Identification Using a CMOS Optical Microsystem”